agileSensorIF

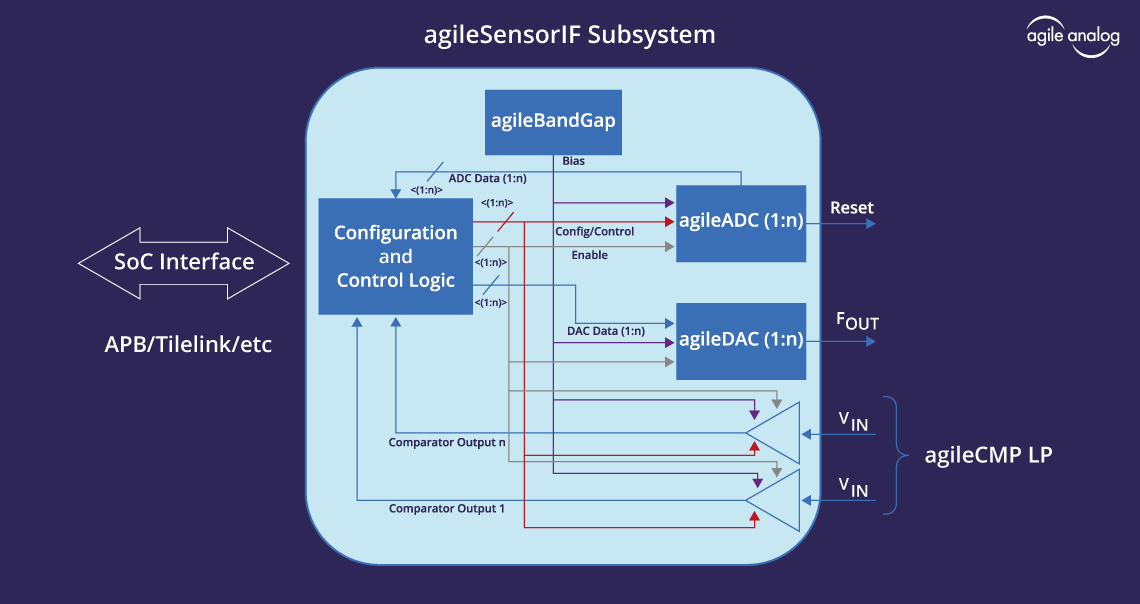

The agileSensorIF Subsystem is an efficient and highly integrated sensor interface for SoCs/ASICs. Featuring multiple Analog-to-Digital Converters (agileADC), Digital-to-Analog Converters (agileDAC), low-power programmable analog comparators (agileCMP_LP), and an associated reference generator (agileREF). The agileSensorIF Subsystem enables easy interaction with the analog world.

The components within the subsystem can be customized to suit a variety of applications. This includes selecting the number of agileADC, agileDAC, and agileCMP_LP blocks, as well as their bit depth and sample rate. This allows the agileSensorIF Subsystem to be perfectly tailored to your exact needs and use case.

Status monitors provide real-time feedback on the current state of the subsystem, ensuring optimal system performance. The monitoring of process, voltage and temperature variations are critical to optimize power and performance for modern SoCs/ASICs, especially for advanced node and FinFET processes.

Agile Analog designs are based on tried and tested architectures to ensure reliability and functionality. Our design methodology is programmatic, systematic and repeatable leading to analog IP that is more verifiable, more robust and more reliable. Our methodology also allows us to quickly re-target our IP to different process options. We support all the major foundries including TSMC, GlobalFoundries, Samsung Foundry and SMIC as well as other IC foundries and manufacturers.

Resolution: up to 12-bits • Sampling rate (Fs)1: up to 64 MSPS • SNR1: Typ 70 dB • ENOB1: Typ 11.3 bits • SFDR1: Typ 90 dBc • INL: +/2 LSB • DNL: +/-1 LSB • Up to 16 input channels

Resolution: up to 12-bits • Sampling rate (Fs)1: up to 20 MSPS • SNR1: Typ 70 dB • INL: +/2 LSB • DNL: +/-1 LSB

Programmable thresholds • Active current: 1.5μA (max) • Detection time: 2μs (typical) • Hysteresis: 20mV • Threshold step size: 56.25mV • Threshold accuracy: 10mV

Block Diagram | Sensor Interface Subsystem | agileSensorIF

Take a look at this selection of Agile Analog marketing content with related information. These press releases offer some interesting insights into our industry collaborations and product development work.